Mar 3 2015

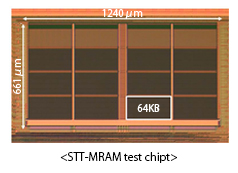

We have developed a spin-transfer torque magnetoresistive random-access memory (STT-MRAM) circuit for use in high-performance processors and system-on-a-chip (SoC) integrated circuits, implementing a 1-Mb class of new magnetic materials. The newly developed memory circuit allows low-power, high-efficiency, high-speed performance in energy-efficient magnetic tunnel junction (MTJ) memory.

The proposed memory circuit provides speed performance capable of 3.3-ns access to in-cache memory. The circuit furthermore consumes approximately 80% less power than conventional static RAM (SRAM) as embedded memory, giving it the best power performance of any type of embedded memory. Details of the proposed technology were presented on February 24 at the 2015 International Solid-state Circuits Conference in San Francisco.

Development background and market trends

The semiconductor SoC market has been expanding in recent years, with demand for various applications, such as “Internet of things” chips, wearable computing, smartphones, and cloud-based datacenters. Such applications have intensified the need for increased performance and lower power consumption. The dominant factor behind semiconductor power consumption is increased SRAM memory capacity and the associated memory power consumption. A problem of particular concern has been the amount of power spent as leakage current within memory circuits. A potential solution to this problem is using nonvolatile memory in place of the volatile memory currently used. To that end, we have been developing a high-speed, low-power magnetic memory, called MTJ.

However, peripheral memory control circuits too consume large amounts of power, so even given a (normally off) low-power memory array circuit, the power consumption of the overall cache memory is not low enough.

Features of the proposed technology

To solve the problems described above, and to make memory control circuit components nearly normally-off, we designed a circuit for sub-100-ns high-speed power shutoff and restoration and confirmed its operation. Specifically, to reduce the time for power restoration after shutoff, we divide power shutoff into seven regions, provide power switches for each region, and then allow power shutoff for regions other than those involved in memory operations. In measured values for the main operational mode, the best time for power restoration was confirmed as 22 ns following power shutoff, which is shorter than the approximately 30 ns average wait time for cache memory access. Furthermore, many innovations further reduce needless power consumption during reads and writes.

The technologies described above have resulted in an approximately 80% reduction in power consumption, as compared to conventional embedded SRAM.

Future developments

The developed magnetic memory technology is being pursued as a fundamental technology development project by the New Energy and Industrial Technology Development Organization. We will continue to improve the developed magnetic memory elements and circuits, with the aim of developing, by project end (fiscal 2015), nonvolatile memory technologies that reduce overall processor power consumption to less than one-tenth that of conventional circuits.