Oct 23 2013

Researchers in electrical and computer engineering at University of California, Santa Barbara have introduced and modeled an integrated circuit design scheme in which transistors and interconnects are monolithically patterned seamlessly on a sheet of graphene, a 2-dimensional plane of carbon atoms. The demonstration offers possibilities for ultra energy-efficient, flexible, and transparent electronics.

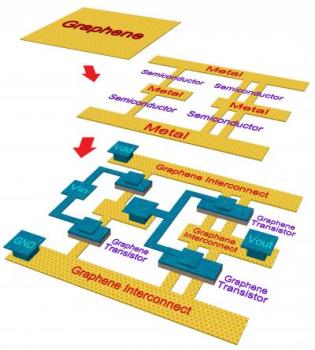

The top schematic is a monolayer graphene sheet. The center schematic displays etched narrow/wide ribbons acting as semiconductor/metal. The bottom schematic is an all-graphene circuit after deposition and patterning of metal and gate dielectric. (credit: UCSB Nanoelectronics Research Lab)

The top schematic is a monolayer graphene sheet. The center schematic displays etched narrow/wide ribbons acting as semiconductor/metal. The bottom schematic is an all-graphene circuit after deposition and patterning of metal and gate dielectric. (credit: UCSB Nanoelectronics Research Lab)

Bulk materials commonly used to make CMOS transitors and interconnects pose fundamental challenges in continuous shrinking of their feature-sizes and suffer from increasing "contact resistance" between them, both of which lead to degrading performance and rising energy consumption. Graphene-based transistors and interconnects are a promising nanoscale technology that could potentially address issues of traditional silicon-based transistors and metal interconnects.

"In addition to its atomically thin and pristine surfaces, graphene has a tunable band gap, which can be adjusted by lithographic sketching of patterns — narrow graphene ribbons can be made semiconducting while wider ribbons are metallic. Hence, contiguous graphene ribbons can be envisioned from the same starting material to design both active and passive devices in a seamless fashion and lower interface/contact resistances," explained Kaustav Banerjee, professor of electrical and computer engineering and director of the Nanoelectronics Research Lab at UCSB. Banerjee's research team also includes UCSB researchers Jiahao Kang, Deblina Sarkar and Yasin Khatami. Their work was recently published in the journal Applied Physics Letters.

"Accurate evaluation of electrical transport through the various graphene nanoribbon based devices and interconnects and across their interfaces was key to our successful circuit design and optimization," explained Jiahao Kang, a PhD student in Banerjee's group and a co-author of the study. Banerjee's group pioneered a methodology using the Non-Equilibrium Green's Function (NEGF) technique to evaluate the performance of such complex circuit schemes involving many heterojunctions. This methodology was used in designing an "all-graphene" logic circuit reported in this study.

"This work has demonstrated a solution for the serious contact resistance problem encounterd in conventional semiconductor technology by providing an innovative idea of using an all-graphene device-interconnect scheme. This will significantly simplify the IC fabrication process of graphene based nanoelectronic devices." commented Philip Kim, professor of physics at Columbia University, and a renowned scientist in the graphene world.

As reported in their study, the proposed all-graphene circuits have achieved 1.7X higher noise margins and 1-2 decades lower static power consumption over current CMOS technology. According to Banerjee, with the ongoing worldwide efforts in patterning and doping of graphene, such circuits can be realized in the near future.

"We hope that this work will encourage and inspire other researchers to explore graphene and beyond-graphene emerging 2-dimensional crystals for designing such 'band-gap engineered' circuits in the near future," added Banerjee.