IMEC successfully transferred MemoryVAM (Memory Variability Aware Modeling), the first EDA tool for statistical memory analysis, to Samsung Electronics. The tool predicts yield loss of SRAMs caused by the process variations of deep-submicron IC technologies.

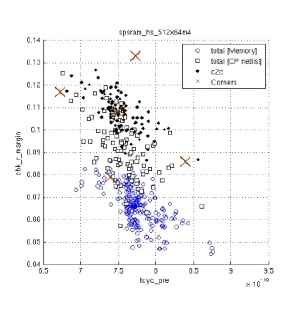

The figure depicts a typical outcome of MemoryVAM for a memory of a partner company of IMEC. Correlations are preserved for both global and local variations of cycle time and read margin for both the CP netlist and the memory. In addition one can see a comparison to a corner-based simulation (crosses). Interestingly, the chip-chip fluctuations have large effect on the cycle time but a small effect on the read margin when compared to local variations. This is logical as the read margin is a voltage difference across a differential signal pair where device matching matters a lot.

The figure depicts a typical outcome of MemoryVAM for a memory of a partner company of IMEC. Correlations are preserved for both global and local variations of cycle time and read margin for both the CP netlist and the memory. In addition one can see a comparison to a corner-based simulation (crosses). Interestingly, the chip-chip fluctuations have large effect on the cycle time but a small effect on the read margin when compared to local variations. This is logical as the read margin is a voltage difference across a differential signal pair where device matching matters a lot.

IMEC’s MemoryVAM is an essential tool to avoid already at design time the most likely reasons for failure, anticipating and correcting weak design spots before tape-out, and hence avoiding redesign spins after processing. The tool also provides key help to memory and system designers to estimate yield loss due to changes of for example cycle time, access time and power consumption (static/dynamic) caused by process variations.

“With MemoryVAM IMEC completes a missing steppingstone in industrial and academic state-of-the-art Design-For-Manufacturing flows which lacked such modeling capabilities for memories;” said Rudy Lauwereins, Vice President Smart Systems Technology Office at IMEC. “This is especially interesting for embedded SRAMs, which are considered to be the most sensitive component to process variations of today’s systems-on-chip. We are excited that the tool is now being successfully used by the product engineering design teams at Samsung Electronics.”

“With collaboration with IMEC, a new novel statistical analysis tool MemoryVAM has become available in our embedded SRAM design.” said Kyu-Myung Choi, Vice President of Design Technology Team at Samsung Electronics. “We expect that MemoryVAM will be helpful for parametric yield modeling of embedded SRAM design and for understanding the unknown gap between design and silicon results due to process variability in deep sub-micron technology below 45nm.”

MemoryVAM is part of IMEC’s Variability Aware Modeling (VAM) flow which is the first holistic flow capable of percolating process variations all the way from the process technology up to the System on a Chip (SoC) level. VAM enables to track the reasons for yield loss and the relative likelihood of such failure. Unlike most of the statistical analysis techniques, VAM is unique in its kind by accurately keeping track of all statistical process, design and environmental correlations tightly linked together and across abstraction levels.

MemoryVAM builds on IMEC’s revolutionary method to analyze performance metrics of semiconductor memories under process variations. The method requires mainly three input items. The first is a transistor level netlist description of a segment of the memory describing all circuitry involved from input to output. The second one is a set of parameters describing the internal architecture of the memory, thus how the memory is built from the segment information, including redundancy and error correction code infrastructure. The third one is information about the variability of the devices and interconnects used in the underlying technology. This information can be provided in either the form of statistical distributions of certain transistor parameters, scattered data obtained via statistical simulation of the device or just plain data set obtained via silicon measurements.

The power of MemoryVAM lies in the analysis of parameters of the memory that can be directly embedded in the input netlist by the designer. These are then used to carry out the implementation of the method, without requiring additional custom modeling steps from the user. The key to this strategy is the ability to complement the analysis of a nominal memory model under test with statistically sampled variants of the devices. This is done by using an in-house developed statistically enhanced Monte Carlo technique, although it also allows the usage of any other available enhanced sampling technique. With this novel and fast analytical technique, statistical information on the critical path percolates to the complete SRAM organization level, resulting in a realistic prediction of the yield as perceived by the memory tester and/or equivalent BIST (built-in-self-testing) technique.