IMEC, a world-leading independent research center in nanoelectronics and nanotechnology, and its 3D integration partners have taped-out Etna, a new 3D chip integrating a commercial DRAM chip on top of a logic IC. The new 3D stack resembles as close as possible to future commercial chips. It consists of a 25µm thick logic die on top of which a commercial DRAM is stacked using through-silicon vias (TSVs) and micro-bumps.

ETNA 3D chip stack paving the way for DRAM on logic integration;

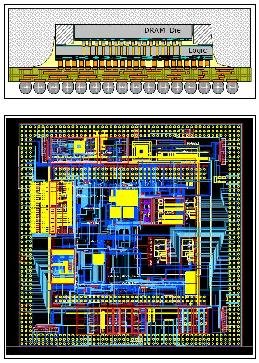

(top) stack configuration; (bottom) layout of the logic die

ETNA 3D chip stack paving the way for DRAM on logic integration;

(top) stack configuration; (bottom) layout of the logic die

The 3D demonstrator mimics all aspects of the approach by stacking an advanced commercial DRAM product chip on IMEC’s proprietary CMOS logic IC. As an example, heaters are integrated to test the impact of hotspot on DRAM refresh times. And, the chip contains test structures for monitoring thermo-mechanical stress in a 3D stack, ESD (electro-static discharge) hazards, electrical characteristics of TSVs and micro-bumps, fault models for TSVs, etc.

The design of the 3D chip is realized together with many players in the 3D integration supply chain. Now, IMEC is manufacturing the logic die in its prototype line, and will be stacking the commercial DRAM chip on top of it. One of IMEC’s 3D integration partners will deliver the DRAM dies, and will test the fabricated 3D stack; two other partners, will package the 3D stack using flip-chip onto a FBGA (fine-pitch ball-grid array) substrate.

“We are excited to achieve this milestone in collaboration with our 3D integration partners including memory suppliers and IC manufacturers. This test-chip is a significant step for the introduction of 3D technology in DRAM-on-logic applications;” said Pol Marchal, principal scientist 3D integration at IMEC.