Researchers of the California Nanosystems Institute at UCLA along with researchers from UCLA Henry Samueli School of Engineering and Applied Science and UCLA Department of Chemistry and Biochemistry have developed a scalable technique for the damage-free fabrication of self-aligned graphene transistors.

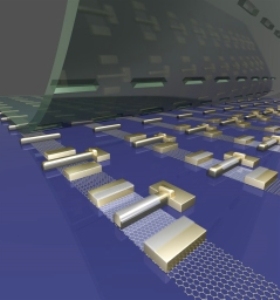

Self-alligning graphene transistors (Credit: UCLA)

Self-alligning graphene transistors (Credit: UCLA)

Graphene is derived from graphite and is a single-layered structure of carbon atoms. Its properties make it an ideal candidate to operate as transistors to facilitate the development of smaller and faster electronic devices.

Large scale fabrication of graphene is impeded by the dwindling scale of electronic devices and graphene’s distinctive properties. When conventional fabrication techniques are employed for graphene manufacture, the performance and lattice shape of graphene often gets damaged in the process that leads to problems such as serial resistance and parasitic capacitance when employed in circuits. The new method involves the use of a sacrificial substrate for carrying out the lithography, deposition and etching steps and subsequent employment of a physical transferring process to integrate the pattern with graphene.

The method paves way for damage-free, self-aligned graphene transistors with a cutoff frequency of 400 MHz, the highest till date for graphene transistors. The results show the potential for graphene in ultra high frequency devices.

The research is funded by the National Institutes of Health, the National Science Foundation and the U.S. Office of Naval Research.