Nano-electronics research center imec announced today at SEMICON West that it has demonstrated concept and feasibilityfor pore-sealing low-k dielectrics in advanced interconnects. The method, based on the self-assembly of an organic monolayer, paves the way to scaling interconnects beyond N5.

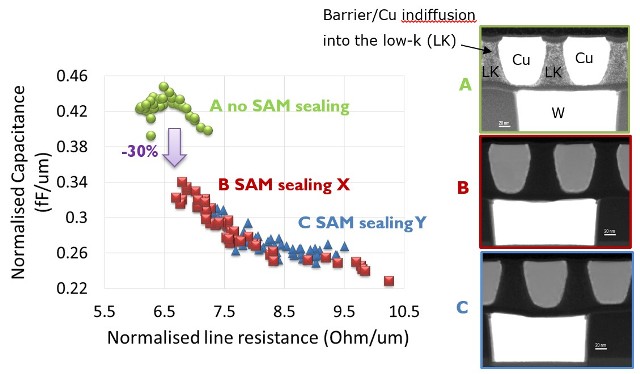

RC plot and HAADF-STEM images illustrating the effectiveness of SAM sealing in preventing metal indiffusion into the ultra-porous low-k film integrated in a 45nm half pitch dual damascene test vehicle. This translates in a 30% decrease in the measured capacitance.

RC plot and HAADF-STEM images illustrating the effectiveness of SAM sealing in preventing metal indiffusion into the ultra-porous low-k film integrated in a 45nm half pitch dual damascene test vehicle. This translates in a 30% decrease in the measured capacitance.

The need for ultra-porous low-k materials as interconnect dielectrics to meet the requirements dictated by the ITRS (International Technology Roadmap for Semiconductors) poses several challenges for successful IC integration. One of the most critical issues is the indiffusion of moisture, ALD/CVD metal barrier precursorsand Cu atoms into the porous low-k materials during processing (low-k pore diameter larger than 3nm, up to 40% porosity). Thisleads toa dramatic increase of the material dielectric constant and leakage current, and to the reduction of the voltage for dielectric breakdown.

Imec has developed a method to seal the pores of the low-k material with a monomolecular organic film.The method not only prevents diffusion of moisture and metal precursors into the low-k material, it also might provide an effective barrier to confine copper within the copper wires and prevent copper diffusion into the low-k material.

Self-assembled monolayers (SAMs)derived from silane precursors, are deposited from vapor phase on 300mm wafers into low-k during chemical vapor or atomic layer deposition and subsequent Cu metallization. The dielectric constant (k) of the resulting sealing layer is 3.5 and a thickness lower than 1.5nm was achieved. This is key to limit the RC delay increase enabling beyond 5nm technology nodes.As a result, a ca. 30% capacitance reduction was observed after SAM pore-sealing was applied. Moreover, a clear positive impact on the low-k breakdown voltage is observed upon sealing.

Imec’s research into advanced interconnects includes key partners as GLOBALFOUNDRIES, INTEL, Micron, Panasonic, Samsung, SK Hynix, Sony, and TSMC.