Oct 7 2016

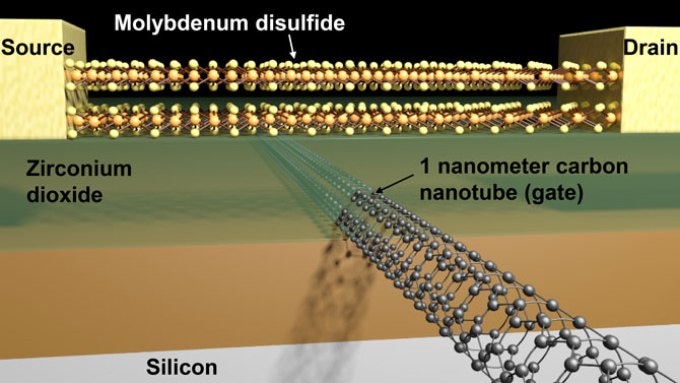

Schematic of a transistor with a molybdenum disulfide channel and 1-nanometer carbon nanotube gate. (Credit: Sujay Desai/UC Berkeley)

Schematic of a transistor with a molybdenum disulfide channel and 1-nanometer carbon nanotube gate. (Credit: Sujay Desai/UC Berkeley)

Reducing the size of components in integrated circuits has been an issue for scientists for over a decade. They were aware that the maximum limit for the size of transistor gates in traditional semiconductors is set at 5 nm, by the laws of physics. This limit is nearly one-fourth of the size of the modern advanced 20 nm gate transistors, available in the market today.

However, some laws are meant be challenged if not broken.

A team headed by Ali Javey, Department of Energy’s Lawrence Berkeley National Laboratory (Berkeley Lab) has created a transistor equipped with an operating 1 nm gate (a single strand of human hair has a thickness of approximately 50,000 nm).

We made the smallest transistor reported to date.The gate length is considered a defining dimension of the transistor. We demonstrated a 1-nanometer-gate transistor, showing that with the choice of proper materials, there is a lot more room to shrink our electronics.

Ali Javey, Berkeley Lab

Javey is the lead principal investigator of the Electronic Materials program in Berkeley Lab’s Materials Science Division.

The researchers achieved this using carbon nanotubes and an engine lubricant, known as molybdenum disulfide (MoS2), which is sold in auto parts shops. MoS2 belongs to a family of materials that have great potential for applications in lasers, solar cells, LEDs and nanoscale transistors, among other devices.

The details of the study have been reported in the journal Science, on October 6. Jeff Bokor, a faculty senior scientist at Berkeley Lab and a professor at UC Berkeley; Chenming Hu, a professor at UC Berkeley; Moon Kim, a professor at the University of Texas at Dallas; and H.S. Philip Wong, a professor at Stanford University, were also a part of the research endeavor.

This development could play a significant role in making Intel co-founder, Gordon Moore’s prediction, a reality. Moore predicted that in two years the density of transistors on integrated circuits would become twice the size, enhancing the performance of mobile phones, laptops, televisions and other electronics.

The semiconductor industry has long assumed that any gate below 5 nanometers wouldn’t work, so anything below that was not even considered. This research shows that sub-5-nanometer gates should not be discounted. Industry has been squeezing every last bit of capability out of silicon. By changing the material from silicon to MoS2, we can make a transistor with a gate that is just 1 nanometer in length, and operate it like a switch.

Sujay Desai, Graduate Student, Berkeley Lab

When ‘Electrons are Out of Control’

There are three terminals - a source, a gate, and a drain - in every transistor. The current flows from the source of the transistor to its drain, and is controlled by the gate that switches on and off depending on the voltage applied.

Although MoS2 and silicon are crystalline lattice structures, the electrons that flow through the silicon are lighter and meet less resistance than those in the MoS2. This is an advantage when the gate is 5n m long or more, but if the length is any shorter the quantum mechanical phenomenon tunneling occurs, and the gate barriers cannot keep the electron flow from barging through the drain.

“This means we can’t turn off the transistors,” said Desai. “The electrons are out of control.”

As the electrons that flow through MoS2 are heavier, gates of shorter lengths can control their flow. It is also possible to scale down the electrons in MoS2 to thin sheets of about 0.65 nm.

These scaled down sheets have a lower dielectric constant, which is an indicator of a material’s potential to store energy in any electric field. The mass of electron, along with the above mentioned properties enhance the control over the flow of current within the transistor when the length of the gate is shrunk to 1 nm.

After deciding on MoS2 as the material for the semiconductor, the gate had to be constructed. It is not easy to construct a 1 nm structure. As traditional lithography techniques are not suited for working with this scale, the engineers employed carbon nanotubes, which are hollow cylindrical tubes with 1 nm diameter.

The researchers then measured the device’s electrical properties to demonstrate that the MoS2 transistor that contained the carbon-nanotube gate was able to efficiently control the electron flow.

This work demonstrated the shortest transistor ever. However, it’s a proof of concept. We have not yet packed these transistors onto a chip, and we haven’t done this billions of times over. We also have not developed self-aligned fabrication schemes for reducing parasitic resistances in the device. But this work is important to show that we are no longer limited to a 5-nanometer gate for our transistors. Moore’s Law can continue a while longer by proper engineering of the semiconductor material and device architecture.

Ali Javey, Berkeley Lab

The Department of Energy’s Basic Energy Sciences program funded the research endeavor.